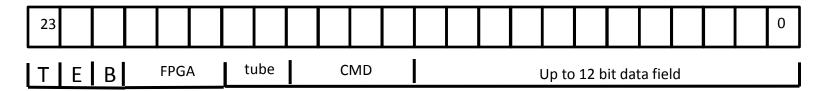

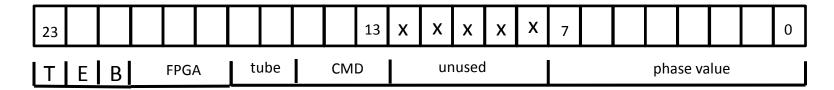

### 24 bit command sent to mainboard FPGA's

- T charge injection timing phase control & adc control

- E daughter board to transmit command to mainboard

- B daughter board to retrieve 12 bits from mainboard

- FPGA which mainboard FPGA should execute the command

- 000 FPGA A0

- 001 FPGA A1

- 010 FPGA B0

- 011 FPGA B1

- 1XX all FPGAs

- Tube which 3in1 card associated with the FPGA to execute the command

- 00 3in1 card far from patch panel

- 01 center 3in1 card

- 10 3in1 nearest patch panel

- 11 all 3 3in1 cards

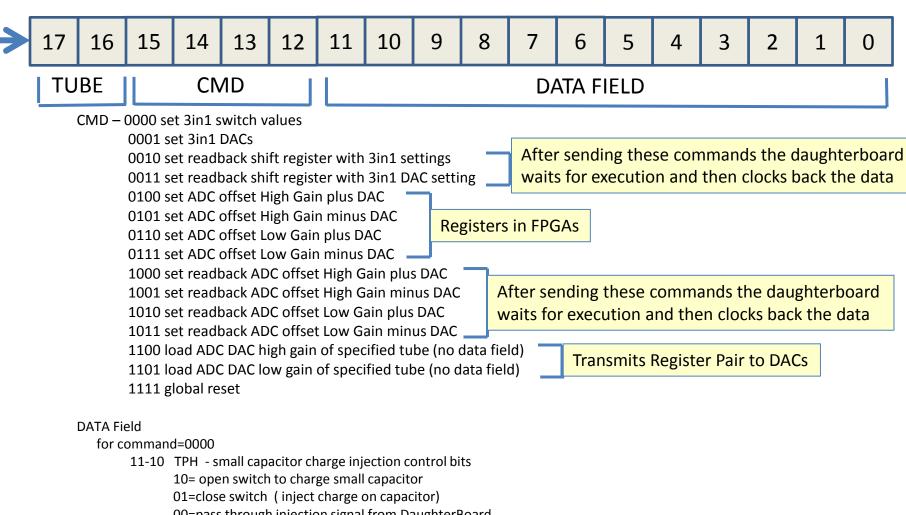

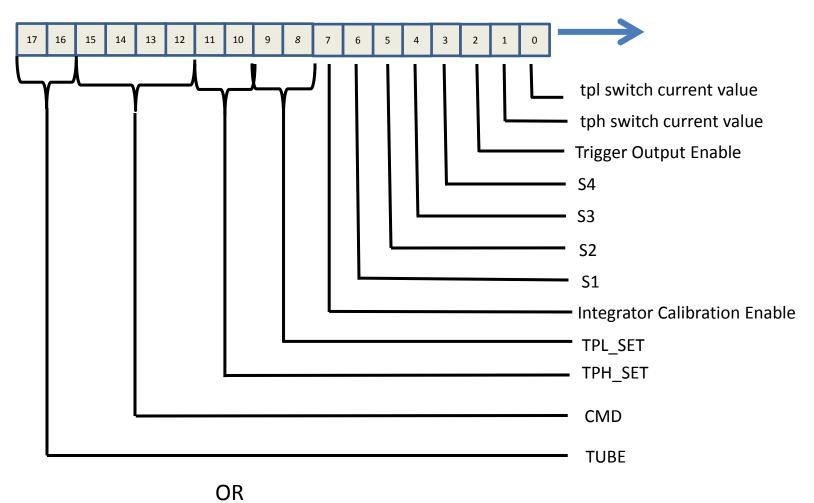

00=pass through injection signal from DaughterBoard

9-8 TPL - large capacitor charge injection control bits

10= open switch to charge small capacitor

01=close switch (inject charge on capacitor)

00=pass through injection signal from DaughterBoard

7 Integrator Calibration Enable

6-3 integrator gain switches S1-S2-S3-S4

2 Trigger Enable

1-0 unused

for DAC set commands

11-0 appropriate 12BIT DAC latched value

# **READBACK Word (18 bits)**

11 downto 0 = 12bit appropriate DAC latched value

# CIS timing phase

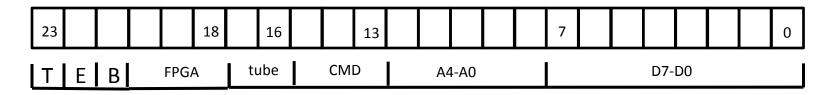

### 24 bit command sent to mainboard FPGA's

| 23    |  |  |      |  |  |      |  |     | 13 | Х      | х | X | х | х | 7           |  |  |  |  |  |  | 0 |

|-------|--|--|------|--|--|------|--|-----|----|--------|---|---|---|---|-------------|--|--|--|--|--|--|---|

| T E B |  |  | FPGA |  |  | tube |  | CMD |    | unused |   |   |   |   | phase value |  |  |  |  |  |  |   |

### **Reset Phase Control**

Set T=1, E=0,FPGA,TUBE,CMD=0

Set Phase for a particular tube

Set T=1, E=0,FPGA,TUBE,CMD=1 data field[5 downto 0] = phase value

Readback Phase (followed by a B=1 command)

Set T=1, E=0,FPGA,TUBE,CMD=2

Note: T=1 commands have a 3 bit CMD field

## **ADC Control**

#### 24 bit command sent to mainboard FPGA's

#### Set ADC mode

Set T=1, E=0,FPGA,TUBE,CMD=3 d0=0 (serial) d0=1 (parallel) parallel is the power on default

# Set ADC control register

Set T=1, E=0,FPGA,TUBE,CMD=4 address=data field[11..8] data=data field[7..0]

Readback ADC register to ADCBACK register

Set T=1, E=0,FPGA,TUBE,CMD=5 address=data field[11..8]

Readback ADCBACK register

Set T=1, E=0,FPGA,TUBE,CMD=6 (follow with a B=1 command)

Note: T=1 commands for the ADCs have a 3 bit CMD field

## 24 bit command sent to mainboard FPGA's

B=1, FPGA=0,1,2, or 3

Daughter board retrieves data from designated FPGA output register.